Site map: All pages

Guides, code examples, and procedures

NI RIO

RIO guide

NI Academic RIO Device

RIO guide

Application examples

RIO guide

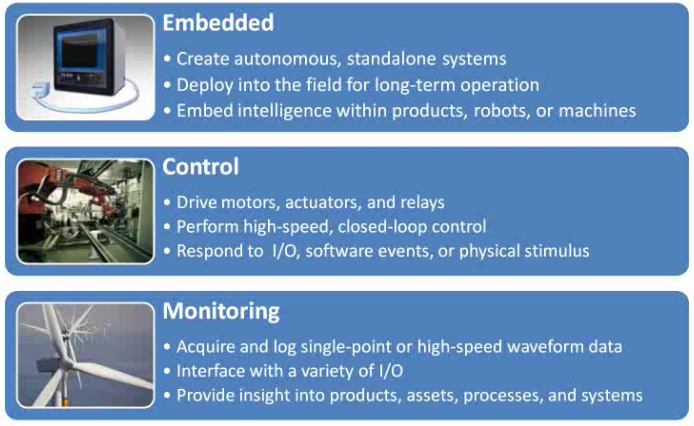

"Embedded Control and Monitoring" video

RIO guide

Make your first RT application

RT procedure

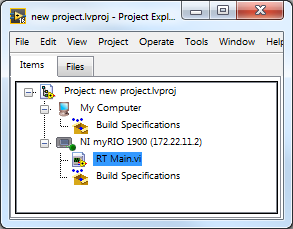

Create a new RT project

RT procedure

Deploy a startup application

RT procedure

RT programming: FPGA personalities

RT guide

I/O Monitor

RT procedure

Develop an FPGA VI

FPGA guide

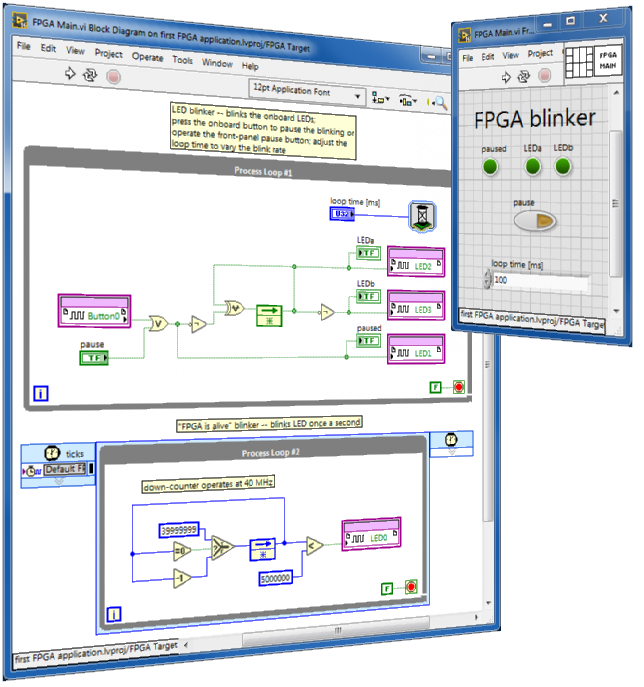

Make your first FPGA application

FPGA procedure

Create a new FPGA project

FPGA procedure

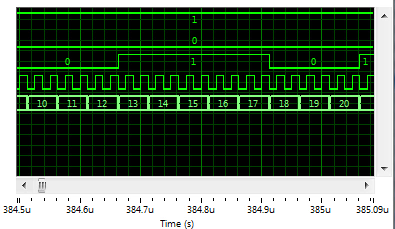

FPGA programming: Simulation techniques

FPGA guide PC guide

Simulate an FPGA VI

FPGA procedure

"Desktop Execution" node as an FPGA VI testbench

FPGA code PC code

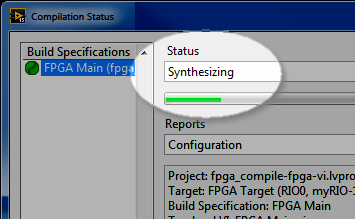

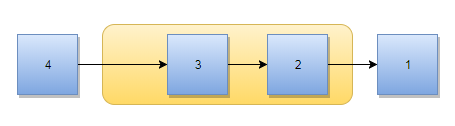

Compile an FPGA VI

FPGA procedure

Derived clock domains

FPGA code

FPGA programming: IP blocks

FPGA guide

Xilinx IP integration

FPGA code

Modify the default Academic RIO Device FPGA personality

FPGA procedure

RT procedures: System administration

RT guide

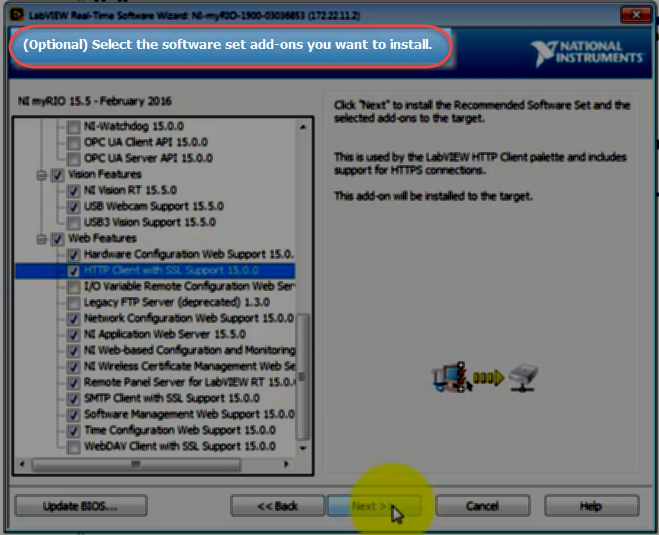

Manage the Academic RIO Device software set add-ons

RT procedure

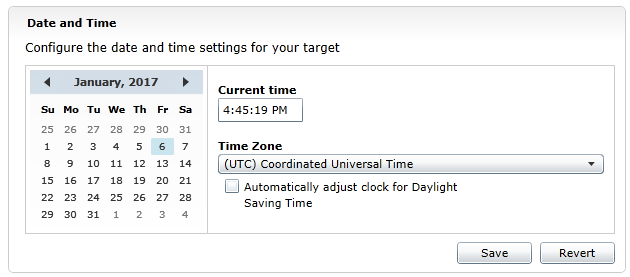

Set RT system time and date from a browser

RT procedure

Set RT system time and date from NI MAX

RT procedure

Set RT system time/date from PC

RT code PC code

RT procedures: File system

RT guide PC guide

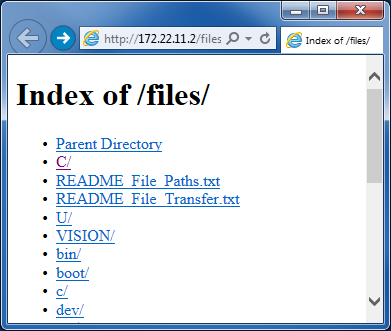

Connect to the Academic RIO Device file system with a web browser

RT procedure PC procedure

Connect to the Academic RIO Device file system with WebDAV

RT procedure PC procedure

Headless datalogger and file I/O

RT code

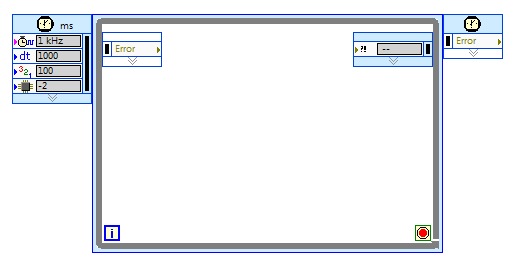

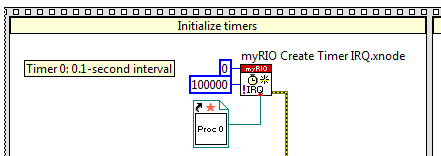

RT programming: Timed loops

RT guide

Timed loop

RT code

Measure loop iteration time

RT code

RT programming: Interrupts

RT guide

RT inter-process communication

RT guide

Local variable (RT)

RT code

Global variable (RT)

RT code

Functional global variable (FGV)

RT code

Queue

RT code

Channel wire

RT code

FPGA inter-process communication

RT guide

Local variable (FPGA)

FPGA code

Global variable (FPGA)

FPGA code

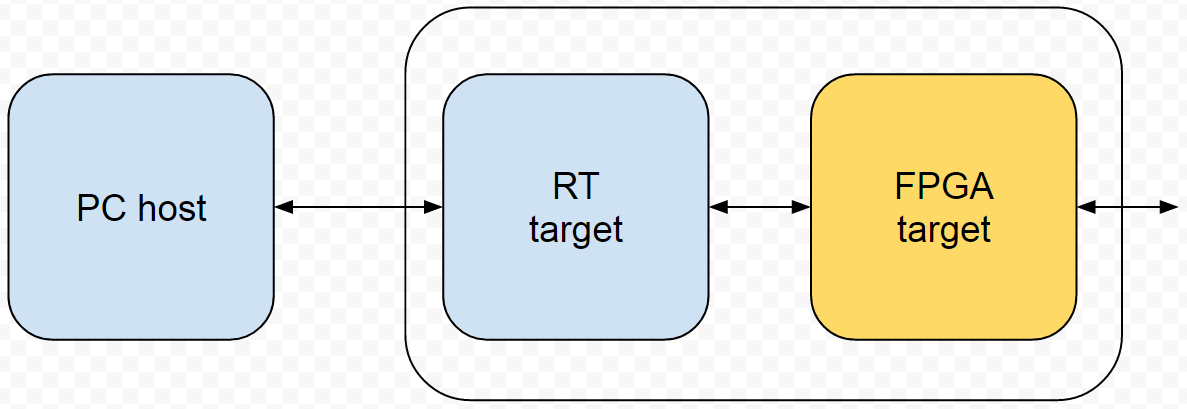

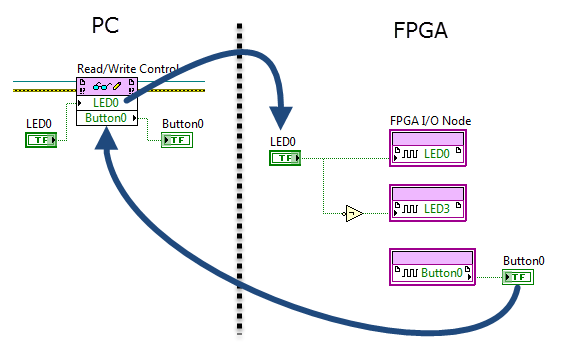

RT/host inter-target communication

RT guide PC guide

Programmatic front-panel communication with RT

FPGA code RT code

RT procedures: Network-published shared variables (NPSVs)

RT guide PC guide

Create a network-published shared variable (NPSV)

RT procedure PC procedure

Bind a PC VI front-panel indicator to a network-published shared variable (NPSV)

RT procedure PC procedure

Network-published shared variable (NPSV)

RT code PC code

Send messages through a network stream channel

RT code PC code

Stream high-speed data through a network stream channel

RT code PC code

Stream high-speed data between FPGA and RT with a DMA FIFO

FPGA code RT code

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

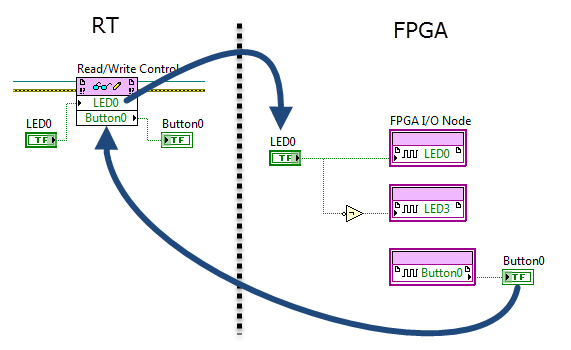

FPGA/RT and FPGA/host inter-target communication

FPGA guide RT guide PC guide

Programmatic front-panel communication with PC

FPGA code PC code

Stream high-speed data between FPGA and PC with a DMA FIFO

FPGA code PC code

RT programming: Queue-based state machines

RT guide PC guide

Queued state machine

RT code

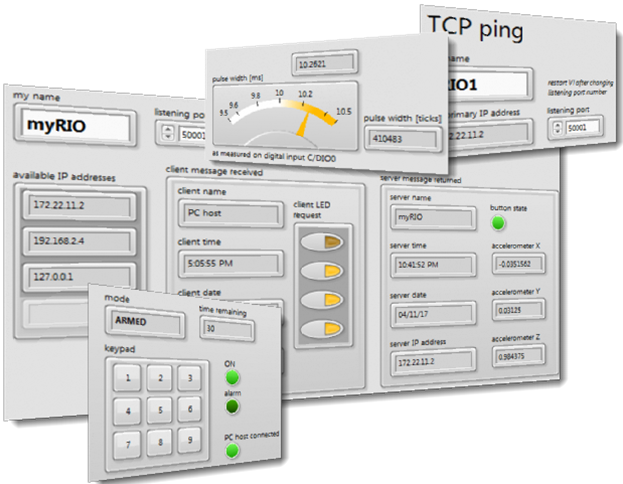

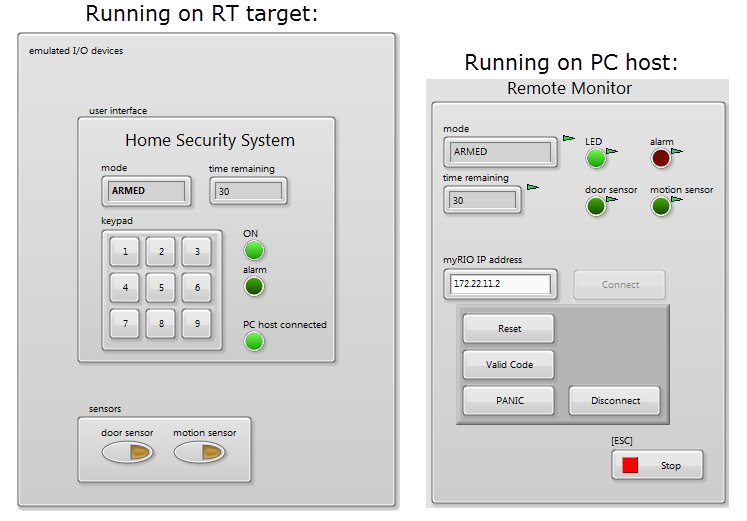

System controller application example: Home Security System

RT code PC code

RT networking: Get connected

RT guide

Connect to a home wireless router

RT procedure

Create an Internet-capable wired network with PC

RT procedure PC procedure

RT networking: IP addresses

RT guide PC guide

Show available IP addresses

RT code PC code

RT networking: email

RT guide

Send an email or text message

RT code

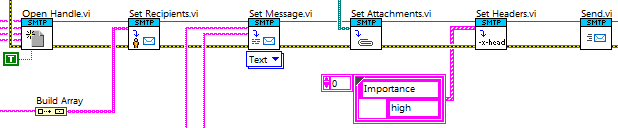

Send a file as an email attachment with high priority (remote webcam photo logger application)

RT code

Check Internet access (HTTP method)

RT code PC code

Check Internet access (TCP method)

RT code PC code

TCP/IP sender and receiver and "TCP ping" application

RT code PC code

TCP client-server

RT code PC code

UDP sender and receiver and "UDP ping" application

RT code PC code

UDP client-server

RT code PC code

RT networking: Web services

RT guide

Web services overview

RT guide

Call a Web service

RT code

Host a Web service

RT code

Tags:

.lvlib.lvproj

Academic RIO

Academic RIO Device

Ad-hoc network

Add on

Admin

Analog I-O

Application example

Architecture

Augmented

Benchmarking

Bitfile

Bound indicator

Breakpoints

Browser

Build specification

Call web service

Channel wire

Client-server

Code reuse

Compile server

Compiler

Configurable

Create project

Custom FPGA

DMA

Data streaming

Datalogger

Deploy

Dequeue

Derived clock domain

Desktop execution node

Deterministic loop

Digital I-O

Distributed System Manager

Dot-decimal notation

ECM

Email attachment

Email headers

Embedded control and monitoring

Enqueue

Ethernet

Execution highlighting

External trigger

FGV

FIFO

FPGA

FPGA application

FPGA design flow

FPGA personality

FPGA simulation

File system

Front Panel Binding Mass Configuration

Functional global variable

Gateway

Global variable

HMI

HTTP

Headless

High-speed processing

High-throughput personality

Host web service

Human-machine interface

I-O Monitor

I-o

IP

IP address

IP blocks

IRQ

Inter-process communication

Inter-target communication

Internet

Internet connection sharing

Interrupt

JSON

LabVIEW FPGA Compile Cloud Service

LabVIEW library

LabVIEW project

Latest value

Local variable

Loop time

Message

MyRIO

MyRIO Toolkit

MyRIO default personality

NCSI

NI MAX

NIST

NPSV

Network

Network streams

Network-published shared variable

Networking

Non-deterministic loop

PC

PC host

PC time source

Parallel process loops

Password

Peripheral testing

Ping

Probes

Process loop

Producer-consumer

Programmatic

QMH

QSM

Queue

Queued message handler

Queued state machine

Quickstart

RIO

RT

RT application

RT-PC

Reboot

Reconfigurable I-O

Register computer

SMS gateway

SMTP

SPSV

Sampling probes

Security

Set time-date

Shared variable

Simulated I-O

Simulation

Simulation mode

Single-process shared variable

Software set

Start-up VI

State machine

Stopping parallel loops

Streaming

System clock

System controller

System date

System time

TCP

Tag

Testbench

Text-based coding

Time stamp

Time zone

Timed loop

Timer

UDP

USBLAN

Uninitialized shift register

VHDL

Web service

Web-based monitoring and configuration

WebDAV

Wired network

Wireless

Wireless router

X-HUB

Xilinx IP

LabVIW block diagram elements:

Binary CounterBoolean Crossing

Build Path

Callback VI Reference

Clear Errors

Close

Close FPGA VI Reference

Close File

Close Handle

Close Variable Connection

Create Network Stream Reader Endpoint

Create Network Stream Writer Endpoint

Create Timer Interrupt

Date-Time To Seconds

Dequeue Element

Desktop Execution node

Destroy Stream Endpoint

Destroy Timer Interrupt

Enqueue Element

Enqueue Element at Opposite End

Error Ring

Event Structure

FIFO Method Node

Feedback Node

First Call?

Flat Sequence Structure

Flatten To JSON

Flush Stream

Format Date-Time String

Format Into File

Format Into String

Get Date-Time In Seconds

Get Date-Time String

Get Notifier Status

Get Number of Records

Get Queue Status

Get Time-Date String

Global Variable

HTTP Get

IP Integration node

IP To String

Initialize Session

Interrupt

Invoke Method

Invoke Node

Join Numbers

Local Variable

Loop Timer

Obtain Notifier

Obtain Queue

Open FPGA VI Reference

Open Handle

Open Variable Connection

Open-Create-Replace Datalog

Property Node

Read Datalog

Read Form Data

Read Multiple Elements from Stream

Read Postdata

Read Single Element from Stream

Read Variable

Read-Write Control

Recursive File List

Register Analog Input Interrupt

Register Digital Input Interrupt

Release Notifier

Release Queue

Restart

Scan From File

Scan From String

Send

Send Email

Send Notification

Set Attachments

Set Custom Bitfile

Set Datalog Position

Set HTTP Response MIME Type

Set Headers

Set Message

Set Recipients

Set Time

Single-Cycle Timed Loop

Split Number

String To IP

TCP Close Connection

TCP Create Listener

TCP Open Connection

TCP Read

TCP Wait On Listener

TCP Write

Tick Count (ms)

Timed Loop

UDP Close

UDP Open

UDP Read

UDP Write

Unflatten From JSON

Unregister Interrupt

Vision Acquisition

Wait Until Next ms Multiple

Write Datalog

Write Multiple Elements to Stream

Write Response

Write Single Element to Stream

Write Variable

Targets:

FPGAPC

RIO

RT

Communications:

FPGA-PCFPGA-RT

Inter-process

Inter-target

Latest value

Message

NPSV

PC-FPGA

Queue

RT-FPGA

RT-PC

Streaming

Tag