RIO Developer Essentials Guide for Academia

RT guide

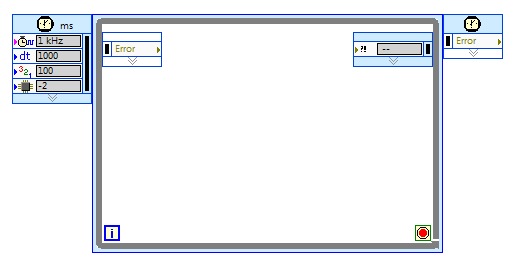

RT programming: Timed loops

A "timed loop" is a while-loop structure that executes at a precise user-specified rate. Timed loop are particularly useful for process control loops that demand a reliable update rate.

Summary

Timed loops operate with a precisely-defined iteration time, and are the primary purpose of a real-time operating system (RTOS) such as the NI Linux Real-Time operating system.

Code examples

- Implement a timed loop, also known as a deterministic process loop, that runs with a precise user-defined time per iteration.

- Use the “Tick Count” function to measure the loop time, i.e., the total elapsed time per iteration of a process loop.

- Observe the dramatic reduction in jitterUnpredictable variation in process loop execution time from one iteration to the next. with this high-precision waveform measurement application example.

For more information

- Creating Deterministic Applications Using the Timed Loop (Real-Time Module) (http://zone.ni.com/reference/en-XX/help/370622P-01/lvrtconcepts/deterministic_apps_timed_loop/)

A brief introduction to deterministic (timed) loops and non-deterministic loops, establishing priority, and partitioning an application into deterministic and non-deterministic components.