Site map: Procedures

Make your first RT application

RT procedure

Create a new RT project

RT procedure

Deploy a startup application

RT procedure

I/O Monitor

RT procedure

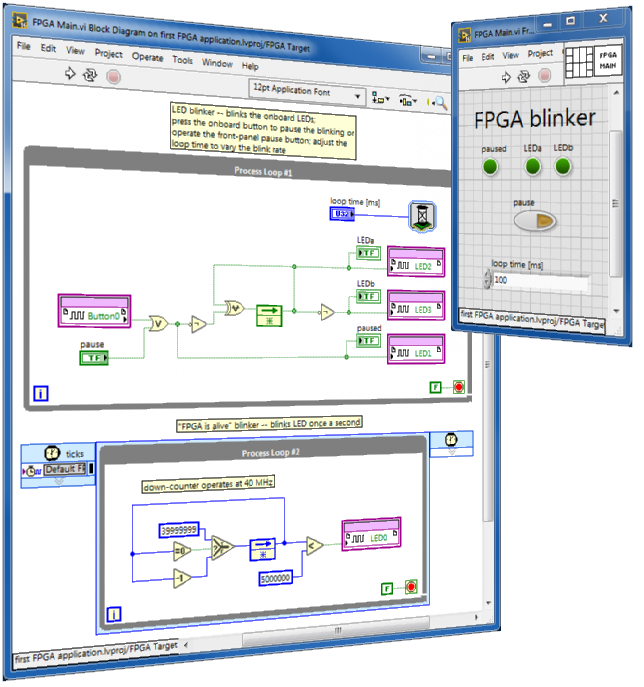

Make your first FPGA application

FPGA procedure

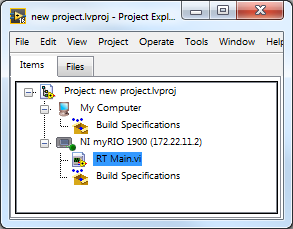

Create a new FPGA project

FPGA procedure

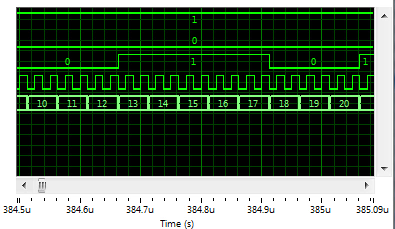

Simulate an FPGA VI

FPGA procedure

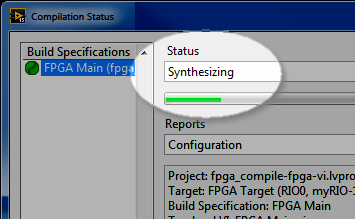

Compile an FPGA VI

FPGA procedure

Modify the default Academic RIO Device FPGA personality

FPGA procedure

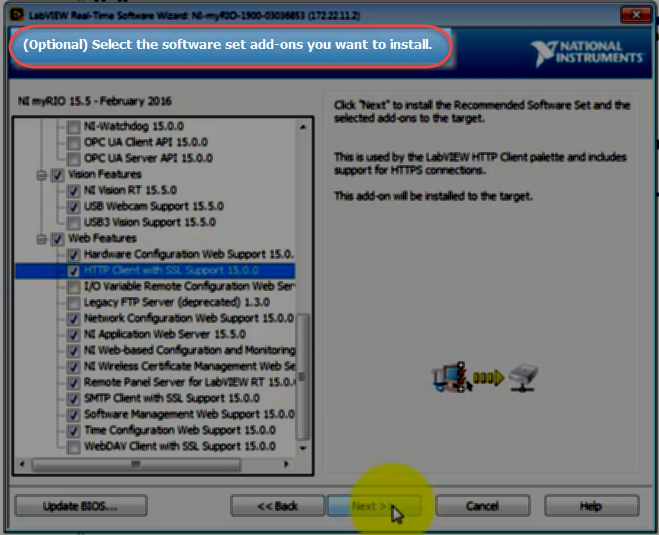

Manage the Academic RIO Device software set add-ons

RT procedure

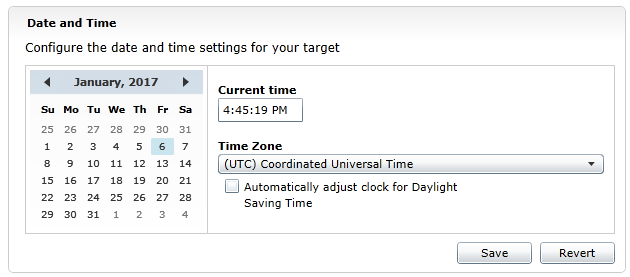

Set RT system time and date from a browser

RT procedure

Set RT system time and date from NI MAX

RT procedure

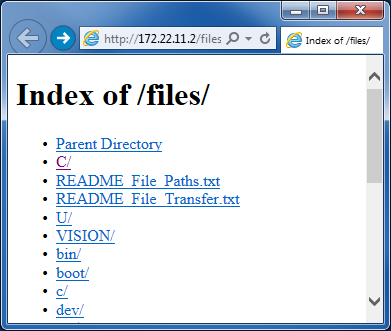

Connect to the Academic RIO Device file system with a web browser

RT procedure PC procedure

Connect to the Academic RIO Device file system with WebDAV

RT procedure PC procedure

Create a network-published shared variable (NPSV)

RT procedure PC procedure

Bind a PC VI front-panel indicator to a network-published shared variable (NPSV)

RT procedure PC procedure

Connect to a home wireless router

RT procedure

Create an Internet-capable wired network with PC

RT procedure PC procedure