RIO Developer Essentials Guide for Academia

"Deterministic loop" tag

RT programming: Timed loops

RT guide

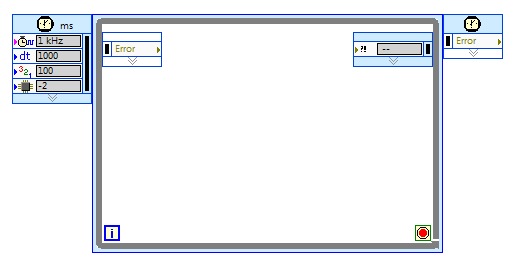

A "timed loop" is a while-loop structure that executes at a precise user-specified rate. Timed loop are particularly useful for process control loops that demand a reliable update rate.

Timed loop

RT code

Use the "Timed Loop" to create a deterministic process loop, i.e., a loop that runs with a precisely-defined time per iteration.

Measure loop iteration time

RT code

Use the "Tick Count" function to measure the total elapsed time per iteration of a process loop.