RIO Developer Essentials Guide for Academia

"Feedback Node" element

Make your first RT application

RT procedure

Follow along with this step-by-step tutorial to make a "hello, world!"-like application to experience the advantages of multiple linked VIs running simultaneously on the real-time (RT) target and desktop computer: (1) "RT Main" runs as the RT target start-up VI, blinks the onboard LEDs, and reads the onboard button; these onboard devices physically connect to the FPGA I/O pins which are accessed with the Academic RIO Device Toolkit Express VIs and default FPGA personality, and (2) "PC Main" VI runs on the desktop computer as a user-friendly human-machine interface (HMI) for remote command and control of "RT Main" through the network via shared variables hosted on the RT target.

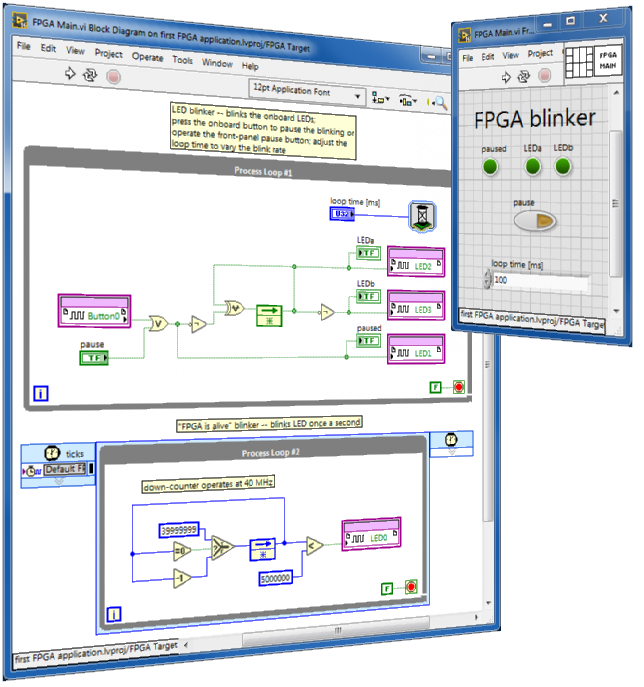

Make your first FPGA application

FPGA procedure

Follow along with this step-by-step tutorial to make a "hello, world!"-like application to experience the advantages of multiple linked VIs running simultaneously on the FPGA target, real-time (RT) target, and desktop computer: (1) "FPGA Main" VI blinks the onboard LEDs and reads the onboard button; these onboard devices physically connect to the FPGA I/O pins, (2) "FPGA testbench" VI runs on the desktop computer for interactive development and debugging of "FPGA Main" in simulation mode prior to compiling to a bitstream file, (3) "RT Main" VI runs as the RT target start-up VI; it runs "FPGA Main", interacts with its front-panel controls/indicators, and communicates with an external desktop computer via network-published shared variables, and (4) "PC Main" VI runs on the desktop computer as a user-friendly human-machine interface (HMI) for remote command and control of "FPGA Main" through the network.

Timed loop

RT code

Use the "Timed Loop" to create a deterministic process loop, i.e., a loop that runs with a precisely-defined time per iteration.

Measure loop iteration time

RT code

Use the "Tick Count" function to measure the total elapsed time per iteration of a process loop.

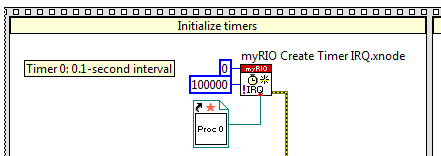

Run a callback VI each time that a digital input transition or an analog input voltage threshold crossing generates an interrupt request (IRQ).

Run a callback VI each time that an FPGA-based interval timer generates an interrupt request (IRQ).

Local variable (RT)

RT code

Use a local variable (front-panel indicator) to communicate between two parallel process loops contained within the same VI, and use a local variable to stop parallel loops with one "stop" button.

Global variable (RT)

RT code

Use a global variable to communicate between two parallel process loops contained within different VIs under the same target, and use a global variable to stop parallel loops with one "stop" button.

Local variable (FPGA)

FPGA code

Use a local variable (front-panel indicator) to communicate between two parallel process loops contained within the same VI.

Global variable (FPGA)

FPGA code

Use a global variable to communicate between two parallel process loops contained within different VIs under the same target.

Send messages through a network stream channel

RT code PC code

Send command and status messages through a low-latency lossless network-based data communication channel between the RT target and PC host system.

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

Load and run a modified version of the default Academic RIO Device personality (FPGA bitfile) augmented by user-defined functionality, for example, to make a high-precision measurement of pulse width.

Queued state machine

RT code

State machines perform system control, data processing, and any task that involves executing a sequence of activities in response to inputs from the surrounding physical system, the user interface, and other processes within the system. The queued state machine is a particular implementation style that is flexible and versatile, easy to maintain, and computationally efficient.

The queued message handler contains multiple process loops operating independently and in parallel that communicate with each other by sending messages through queues. Each process is a well-defined task implemented by the "Queued State Machine" design pattern. Breaking up the system into self-contained tasks greatly simplifies the design of complex systems.

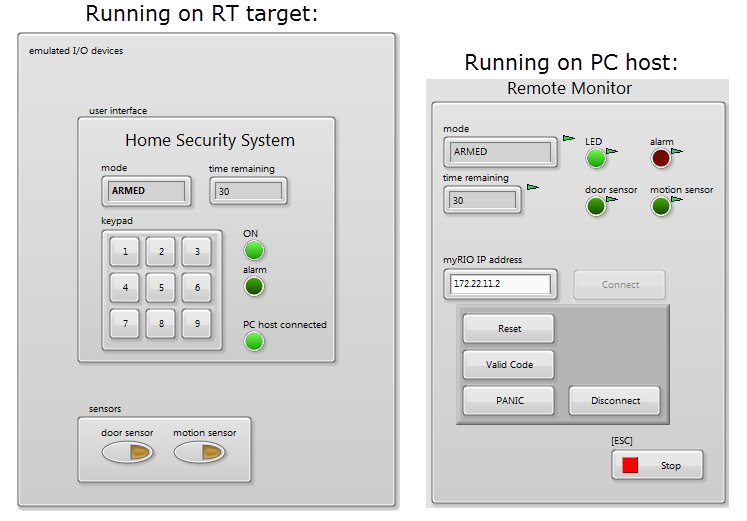

System controller application example: Home Security System

RT code PC code

Example of a complete RT system controller based on the Queued Message Handler (QMH) design pattern with multiple parallel task loops implementing behaviors with queued state machines (QSMs), various inter-process communication techniques (queues and local variables), and inter-target communication techniques (network-published shared variables (NPSVs) and network streams). The PC host human-machine interface (HMI) can remotely connect to the system through the network, monitor the status of the security system, and control it remotely.