RIO Developer Essentials Guide for Academia

"Read-Write Control" element

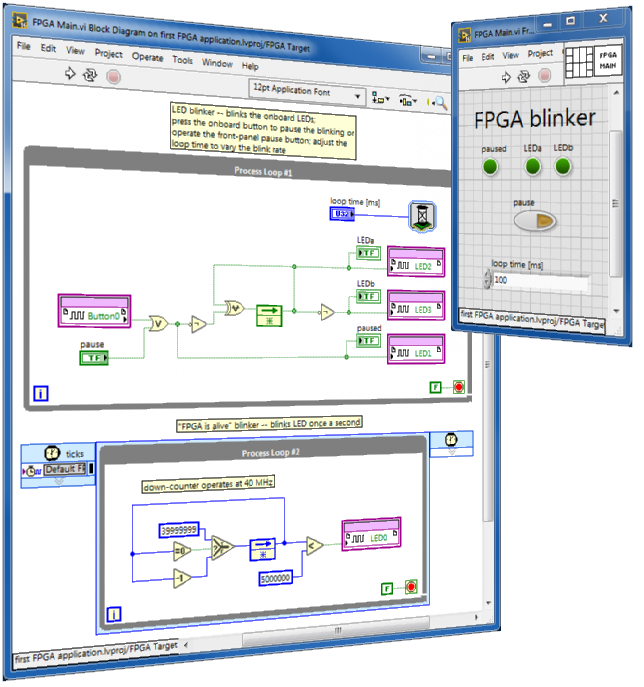

Make your first FPGA application

FPGA procedure

Follow along with this step-by-step tutorial to make a "hello, world!"-like application to experience the advantages of multiple linked VIs running simultaneously on the FPGA target, real-time (RT) target, and desktop computer: (1) "FPGA Main" VI blinks the onboard LEDs and reads the onboard button; these onboard devices physically connect to the FPGA I/O pins, (2) "FPGA testbench" VI runs on the desktop computer for interactive development and debugging of "FPGA Main" in simulation mode prior to compiling to a bitstream file, (3) "RT Main" VI runs as the RT target start-up VI; it runs "FPGA Main", interacts with its front-panel controls/indicators, and communicates with an external desktop computer via network-published shared variables, and (4) "PC Main" VI runs on the desktop computer as a user-friendly human-machine interface (HMI) for remote command and control of "FPGA Main" through the network.

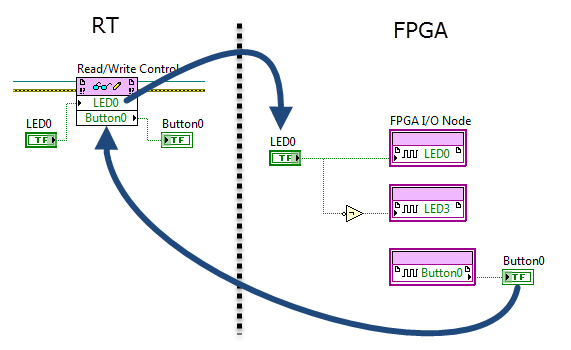

Programmatic front-panel communication with RT

FPGA code RT code

The RT VI operates (writes) the front-panel controls of the FPGA VI and reads its indicators.

Stream high-speed data through a network stream channel

RT code PC code

Efficiently transfer blocks of data between the RT and PC by network streams.

Stream high-speed data between FPGA and RT with a DMA FIFO

FPGA code RT code

Efficiently transfer blocks of data between the RT and FPGA by direct memory access (DMA) first-in first-out (FIFO) buffers.

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

Load and run a modified version of the default Academic RIO Device personality (FPGA bitfile) augmented by user-defined functionality, for example, to make a high-precision measurement of pulse width.

FPGA/RT and FPGA/host inter-target communication

FPGA guide RT guide PC guide

Transfer data, commands, and status between the FPGA target and a host system (RT or PC).

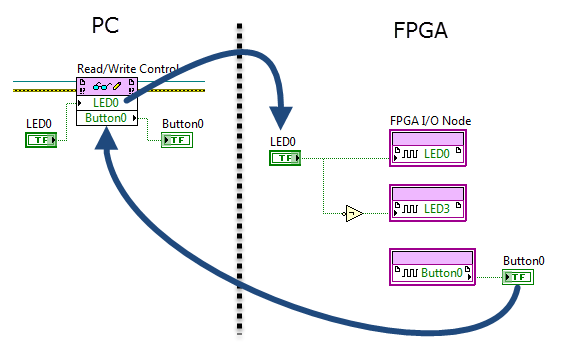

Programmatic front-panel communication with PC

FPGA code PC code

The PC VI operates (writes) the front-panel controls of the FPGA VI and reads its indicators.

Stream high-speed data between FPGA and PC with a DMA FIFO

FPGA code PC code

Efficiently transfer blocks of data between the PC and FPGA by direct memory access (DMA) first-in first-out (FIFO) buffers.