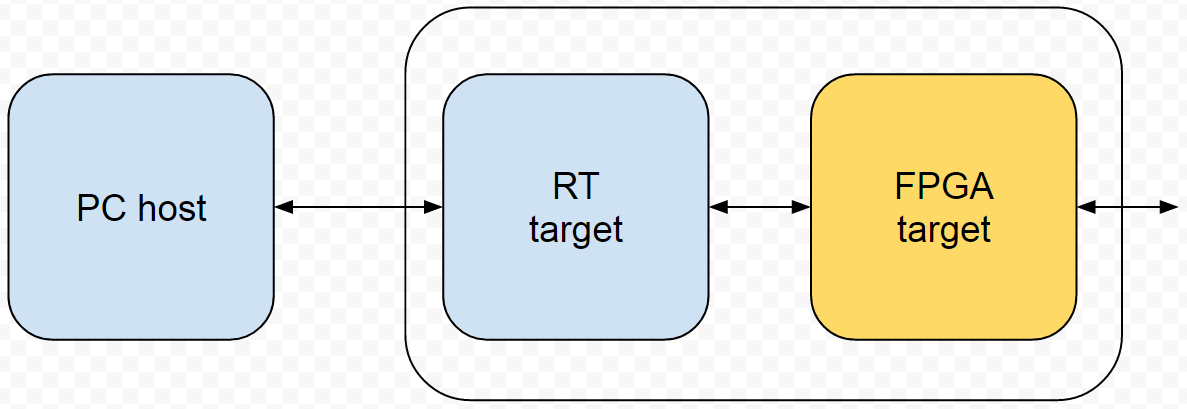

RIO Developer Essentials Guide for Academia

"Derived clock domain" tag

Develop an FPGA VI

FPGA guide

Develop your own FPGA-targeted VI to take advantage of the unique capabilities of the FPGA target such as high-speed I/O, precision I/O timing, parallel processing, and functionality not offered by the RT processor and Academic RIO Device Toolkit default personality; you can also augment the default personality with your needed capability.

Derived clock domains

FPGA code

Use a derived clock domain to effectively speed up or slow down the FPGA's 40-MHz clock for a selected portion of the FPGA block diagram.