RIO Developer Essentials Guide for Academia

"MyRIO default personality" tag

RT programming: FPGA personalities

RT guide

The FPGA "personality" (bitstream configuration file) determines how the RT target interacts with peripheral devices. The personality can also implement custom functionality.

Modify the default Academic RIO Device FPGA personality

FPGA procedure

Add your own functionality to the default Academic RIO Device FPGA "personality" (bitfile) to retain selected Device Express VI capabilities.

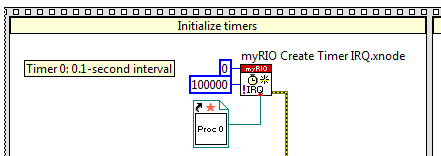

RT programming: Interrupts

RT guide

Use an onboard timer or an external event interrupt request (IRQ) to immediately execute a task.

Run a callback VI each time that a digital input transition or an analog input voltage threshold crossing generates an interrupt request (IRQ).

Run a callback VI each time that an FPGA-based interval timer generates an interrupt request (IRQ).

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

Load and run a modified version of the default Academic RIO Device personality (FPGA bitfile) augmented by user-defined functionality, for example, to make a high-precision measurement of pulse width.