RIO Developer Essentials Guide for Academia

"RT-FPGA" communication

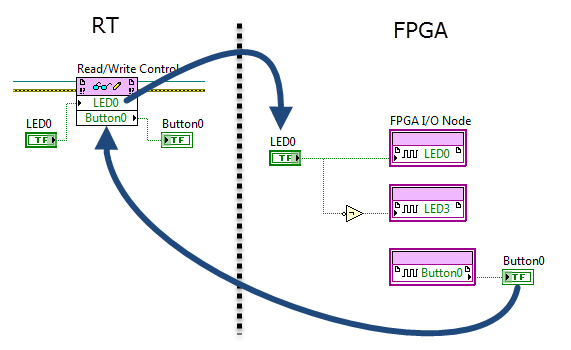

Programmatic front-panel communication with RT

FPGA code RT code

The RT VI operates (writes) the front-panel controls of the FPGA VI and reads its indicators.

Stream high-speed data between FPGA and RT with a DMA FIFO

FPGA code RT code

Efficiently transfer blocks of data between the RT and FPGA by direct memory access (DMA) first-in first-out (FIFO) buffers.

Augmented default Academic RIO Device FPGA personality and high-precision waveform measurement application example

FPGA code RT code

Load and run a modified version of the default Academic RIO Device personality (FPGA bitfile) augmented by user-defined functionality, for example, to make a high-precision measurement of pulse width.